Preliminary

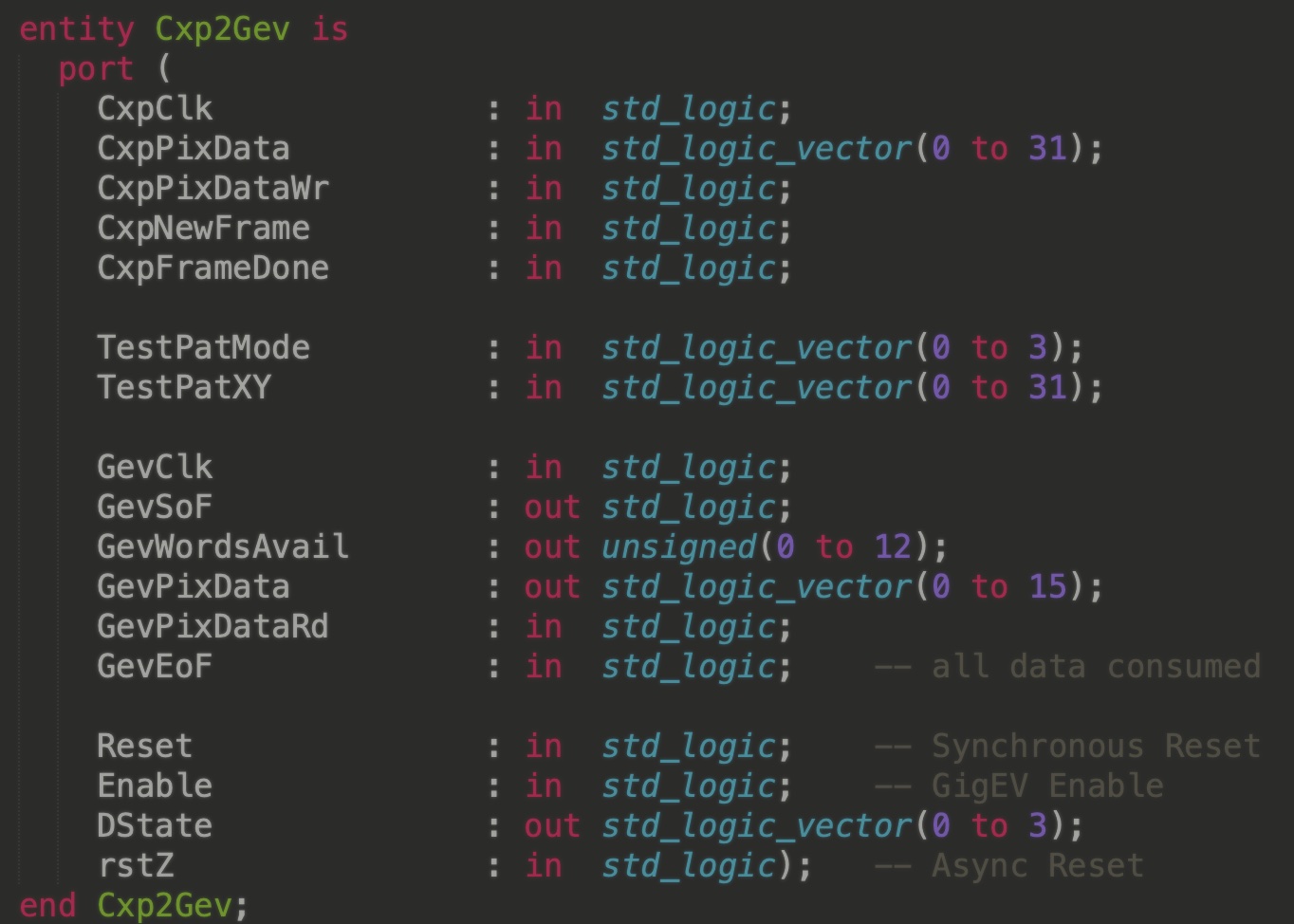

GigEVision Camera (device) FPGA IP

- GVSP stream packet generation

- GVCP control packets routed to/from microcontroller

- Implemented for 1000BASE-T or 2.5GBASE-T PHY

- SGMII+ interface to PHY over FPGA Generic 8B/10B SerDes

- Capable of any GigEVison pixel format

- Pixel FIFO input for integration

- Chunk data capable

- Serial port for control and monitoring

GigEVision Camera (device) Embedded Software

- Ethernet stack and GenICam (GVCP) processor using microcontroller

- DHCP, ARP, IP, UDP, Ping, Link Local addressing, etc. supported by stack

- Developed for TI ARM M4 external microcontroller (for lowest cost)

- Porting to integrated RISC-V FPGA soft controller implementation (for least board space)

- Interfaces with FPGA via RMII 6 wire Ethernet PHY interface

- Compliant GigEVision GenICam control functionality

- GenICam .xml file held in SPI flash

GigEVision Host Firmware

- Currently not available; in planning phase.

Multi-Platform FPGA Compatible

- Currently implemented on Lattice ECP5 (low cost)

- Generic Tecphos firmware libaries will compile for any architecture

FPGA Requirements

- SerDes compatible with Ethernet SGMII 8B/10B data rates

License

- Code status is pre-production. Looking for a partner to assist with production validation in exchange for reduced license fee.

- Standard license is per project with no per-unit fees

- Pre-compiled modules and source code licenses available

- Licenses include 8 hours of customization

- Licenses include one year of support

- License discounts for multiple licenses